Low jitter clocking for Altera Agilex9 Direct RF FPGAs

A. Introduction

Direct RF sampling is known to bring significant advantages over traditional heterodyne implementations, which require additional analog components such as mixers, filters and local oscillators for intermediate frequency signal conversion. As the analog front-end is greatly simplified, noise, power and the overall footprint are also reduced, leading to benefits to the overall system performance. Thanks to the advances in ADC-DAC sampling speed and capabilities, it is now possible to bring analog signal processing to the digital domain, taking advantage of Moore scaling and of the higher flexibility of digital signal processing.

Despite bringing clear advantages, direct RF sampling has its own challenges that need to be taken into account while designing a system, be it a single-module DUT or a multi-module phase array detector. Sampling rates of tens of GSPS, bandwidths of tens of GHz and high resolutions over multiple channels catch our eye when we look at product tables from FPGA vendors, but what are the caveats?

To fully exploit its capabilities without sacrificing on performance, the design of a direct RF system should take the following constraints into account:

- High-frequency and high-quality clock signals are required. Therefore, dedicated clocking solutions need to be systematically characterized in terms of noise, stability and flexibility

- Signal integrity needs to be under control up to tens of GHz and it needs to be evaluated both at PCB layout stage with simulation tools and thoroughly measured as the first PCB samples are manufactured

- Complex data processing is still required in the digital domain despite the fact that complex components have been removed from the analog domain

- Thermal management needs to be planned at early design stages to accomplish reliable heat dissipation for dense and space-constrained systems.

The following sections will focus on clock architectures required for RF applications using Altera Direct RF FPGA , leaving the remaining points of the list above for future discussion.

B. Key role of clocks in RF applications

Regardless of the vendor, all RFSoCs require three main clock signals to operate correctly: a high-frequency sampling clock or PLL reference clock, ranging from the hundreds of MHz to the tens of GHz; a clock to run the RF IP logic, in the hundreds of MHz; and a slower synchronization clock or pulse. Details about clock architectures will be discussed in the following sections, but regardless of the specifics of the clock sources, it is safe to assume that high quality clocks are needed to run ADCs, DACs and the related logic, ensuring good performance of the whole system. But what parameters characterize a clock and what makes it high-quality?

The main parameter of a clock is its frequency, which determines how many clock cycles are present per unit of time. Clock signals come in different shapes, sinusoidal or square, in different modes, single-ended or differential, and in different formats, HCMOS, LVCMOS, LVDS, CML, etc. For sake of simplicity, in the following discussion, a clock is defined as a signal that repeats over time with a certain frequency, leaving shape, voltage levels and modes aside. Another key parameter characterizing clock signals is the rise/fall time or slew rate. All these terms refer to the speed, usually expressed in V/us, at which a signal goes from a low state to high state.

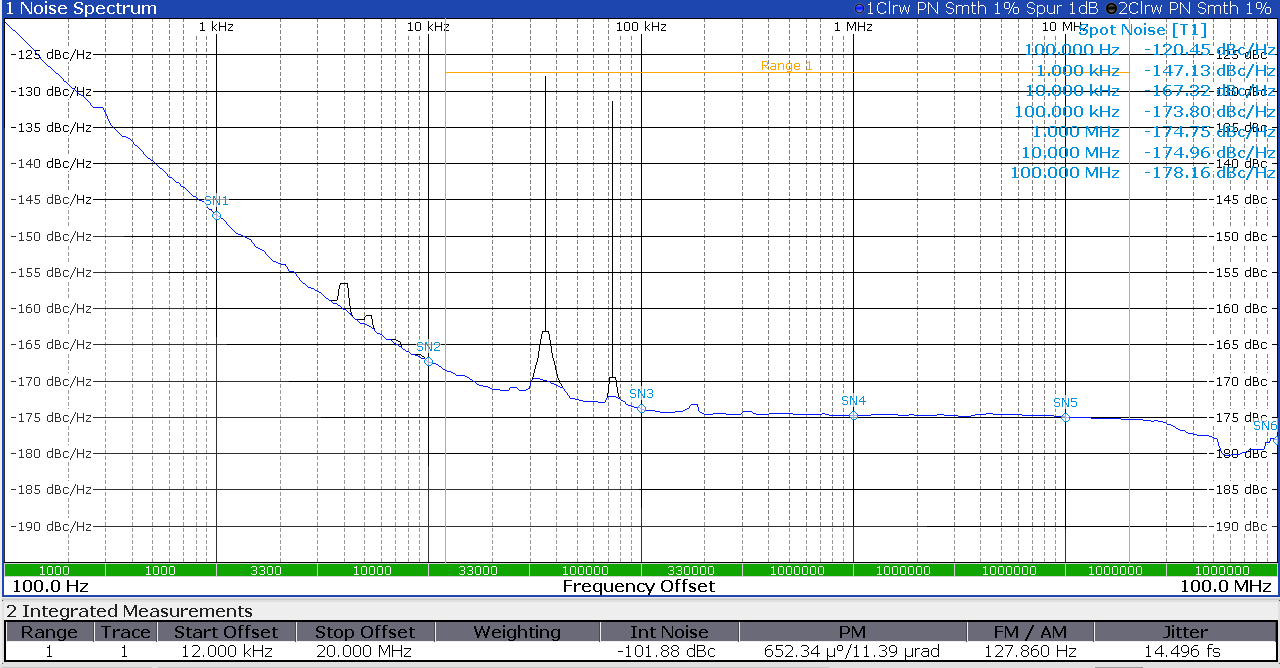

Clock quality can be measured in terms of short-term and long-term stability. Short-term stability is usually evaluated measuring phase noise. To understand phase noise, let’s start from the time-domain representation of a sine waveform

where A is the amplitude, f0 is the frequency and t is time. Phase noise appears as a time-dependent additive phase, as follows

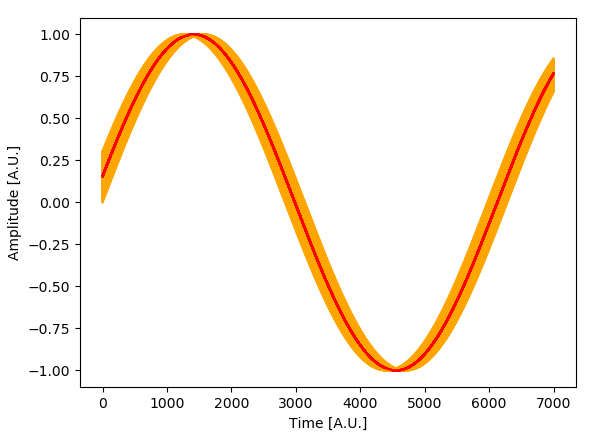

The left plot in Fig. 1 shows the effect of phase noise in time domain which results in a time-dependent shift (orange band) of the original sine wave (red curve). Seen in the frequency domain a pure sine wave is represented by a sharp peak which is broader due to the presence of phase noise, as shown in the right plot in Fig. 1. Phase noise is defined as the power relative to the carrier and measured at a certain offset with respect to the carrier frequency. Phase noise is measured in 1Hz intervals and it is expressed in units of dBc/Hz.

Figure 1: Phase noise in time domain (left) and frequency domain (right).

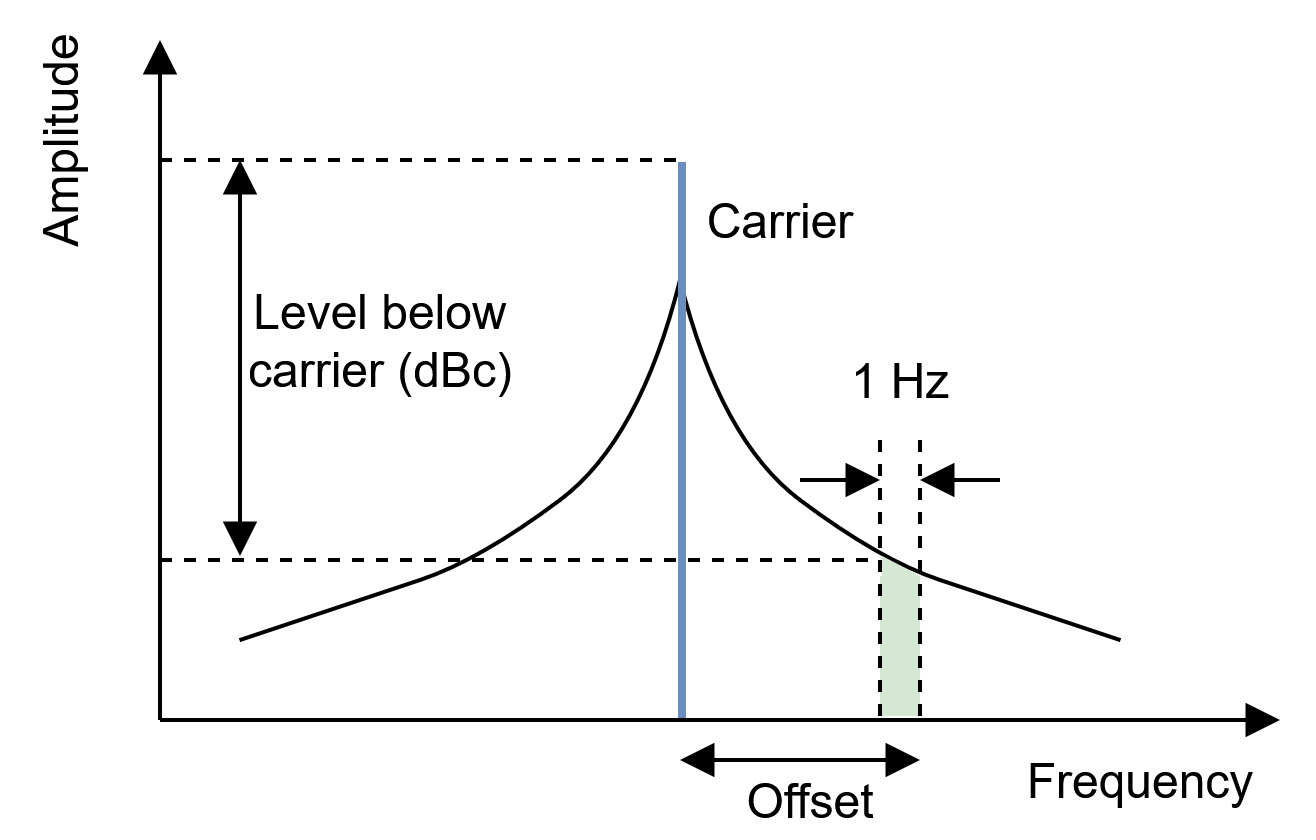

Phase noise is typically measured using phase noise analyzers, and in particular taking advantage of the cross-correlation method which improves accuracy and sensitivity of measurements by minimizing the impact of local oscillators within the measurement equipment. Figure 2 shows a typical single-side-band phase noise profile of a 125 MHz voltage-controlled crystal oscillator (VCXO). The measurement is performed using a Rohde & Schwarz FSWP-50 phase noise analyzer that leverages the cross-correlation method to measure phase noise values as low as -175 dBc/Hz.

Figure 2: Phase noise measurement of a 125MHz VCXO.

Oscillators phase noise is typically shaped by two main noise sources, flicker noise and white noise. Flicker noise has a 1/f spectrum and shapes phase noise at low frequency offsets whereas white noise has a flat spectrum and is spread equally over all frequency offsets.

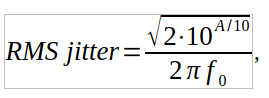

Another common metric that is used to quantify short term stability of clock signals is jitter. Jitter is computed from the phase noise profile using the following equation

where A is the area under the phase noise profile and f0 is the carrier frequency. Figure 2 shows that the characterized VCXO has a jitter of around 14.5fs.

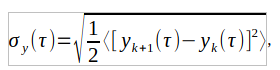

Long term stability is also a key component in determining the quality of a clock source and is usually evaluated using Allan deviation plots. The mathematical derivation of Allan deviation is outside the scope of this article; however, there are a few points worth considering.

The typical phase noise profile (see an example in Fig. 2) shows the presence of flicker noise in addition to white noise. The flicker noise power spectrum, being proportional to 1/f, diverges at low frequencies and, as a consequence, it leads to a standard deviation that increases unboundedly with measurement time. Allan deviation is particularly useful when traditional statistical estimators, such as the standard deviation, do not converge. Allan deviation is a two-sample estimator defined as follows

where yk(τ) are the averaged fractional frequency deviations taken over intervals of duration τ and angle brackets represent the expectation value1. Figure 3 shows the Allan deviation plot of a 125MHz VCXO.

Figure 3: Allan deviation measurement of a 125MHz VCXO.

Besides mathematical and statistical considerations, Allan deviation plots are useful to identify the different noise mechanisms that are at play in a system under study. Considering a noise power spectrum S(f) ~ fα the Allan deviation is proportional to τμ/2, where μ = -α -1. Taking white noise as an example, its spectrum is characterized by

α = 0 and so μ = -1. Therefore the Allan deviation decreases as τ increases as expected, since the effect of uncorrelated white noise is “averaged-out” as the interval τ over which the average is taken increases. Table 1 shows the most common power-law noise processes and the corresponding slope they have in an Allan deviation plot.

|

Power spectrum α |

Allan deviation slope μ |

|

|

White phase noise |

2 |

-3/2 |

|

Quantization noise |

1 |

-1 |

|

Gaussian noise |

0 |

-1/2 |

|

Flicker noise |

-1 |

0 |

|

Brownian noise |

-2 |

1/2 |

|

Steady drift |

-3 |

1 |

Table 1: Common noise types, their spectra and Allan deviation behaviors.

For the sake of simplicity non-overlapping Allan deviation is considered. However overlapping Allan deviation is preferred over the non-overlapping one as it has lower statistical uncertainty.

C. Components of Direct RF FPGA clock architectures

Having discussed the key factors that need to be considered while characterizing clock sources, we can now move to clock architectures for RFSoC systems, starting from their main components. Typically RFSoC clock architectures are made of two main components, a clock reference and one or multiple phase-locked loop ICs (PLLs).

The reference represents the root of the clock tree and it usually consists of a crystal oscillator (XO) that generates a clock with fixed frequency, between few MHz and hundreds of MHz. Since all other clocks are derived from this reference, it is crucial to choose the reference according to the system requirements and characterize it as described in the previous section. Different types of references are available, and they typically belong to one of the following families:

- Voltage-controlled crystal oscillators (VCXO) have adjustable output frequencies based on the voltage applied to a control line

- Temperature-controlled crystal oscillators (TCXO) consist of a VCXO with a temperature sensitive network that tune the control voltage to compensate for temperature changes

- Oven-controlled crystal oscillators (OCXO) use an internal oven to maintain a constant temperature during the operation of the device

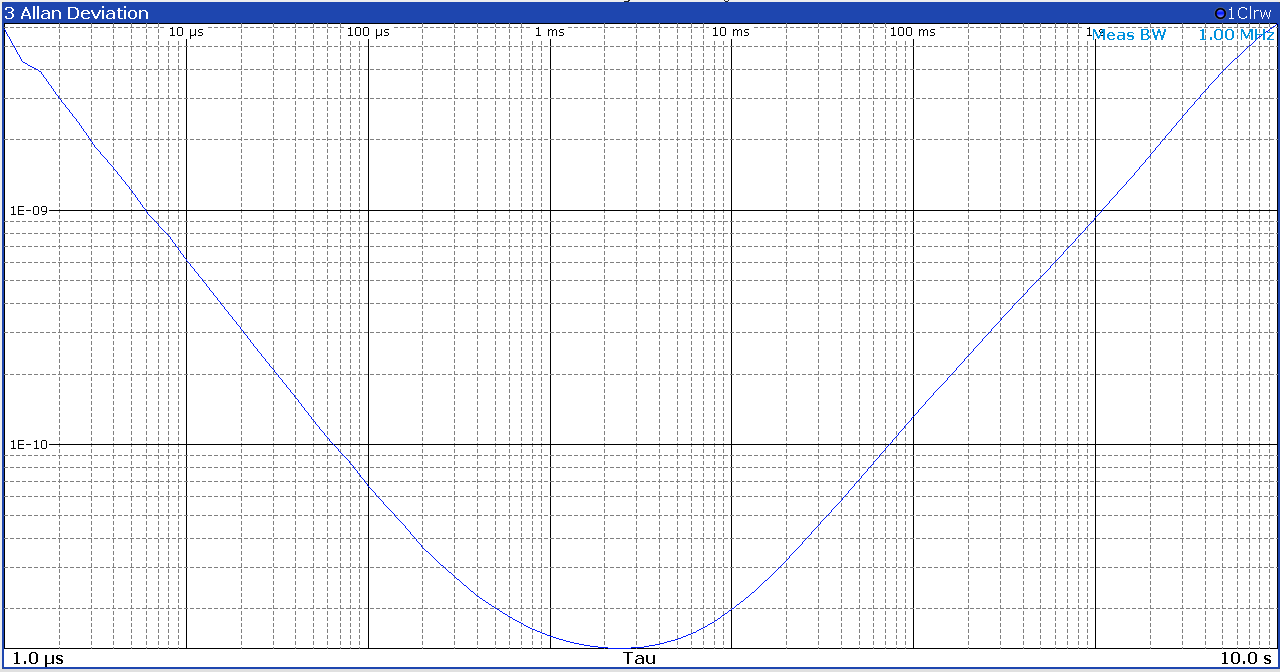

The clock reference output is then fed into one or multiple PLLs to generate clock signals with different frequencies, usually higher than the one generated by the reference. PLLs exist in different types but they share the same working principle based on a feedback control loop: the phase of the input reference clock (θREF) is compared to the one of the clock signal generated by the PLL (θ0UT). Differences in the phase lead to adjustments of the voltage control line of a voltage-controlled oscillator (VCO) until the phases match and the PLL is locked. Figure 4 shows the main building blocks of a PLL which are the following:

- Phase frequency detector (PFD) detects the phase difference between the reference and the feedback signal and generates a pulse to correct this difference

- Charge pump (CP) converts the PFD output into a current pulse that is fed into the loop filter

- Loop filter consists of passive components, typically resistor and capacitors, in a low-pass filter configuration to filter the CP output and drive the VCO control line

- VCO generates the output frequency

- Feedback divider takes the VCO output signal and divides it to obtain the same frequency as of the input reference

Figure 4: Block diagram of a PLL.

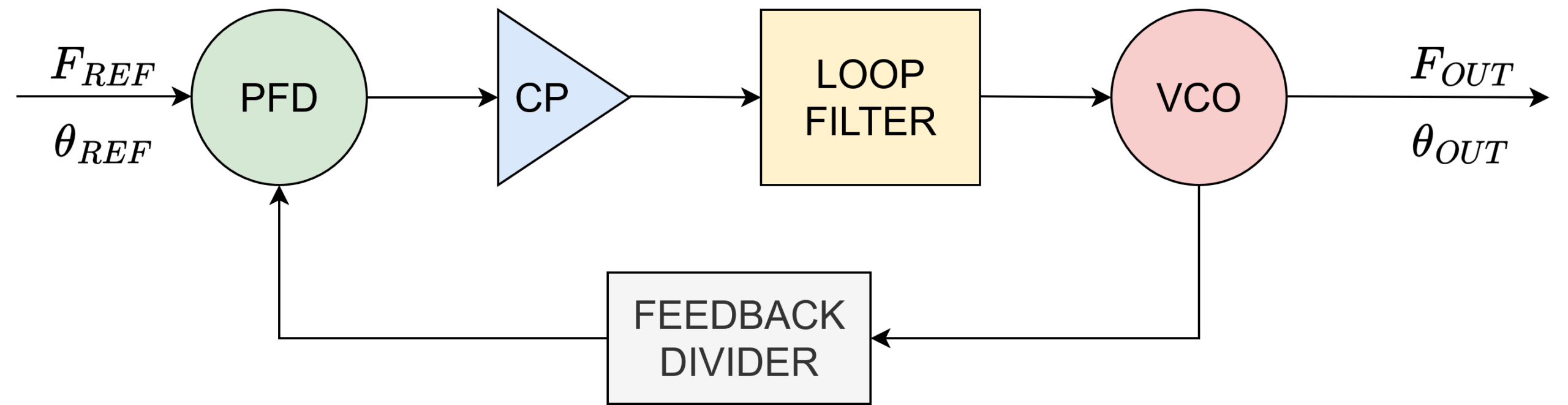

The different components within a PLL determine the overall phase noise of output clock signal. Figure 5 shows an example phase noise simulated behavior of a PLL and the breakdown into the main contributions. At low frequency offsets the total phase noise is dominated by the input reference noise, whereas at mid offsets the VCO dominates the overall phase-noise shape. At high frequency offsets the phase noise is usually driven by the noise floor.

Figure 5: Phase noise simulated behavior of a PLL and breakdown into main contributions.

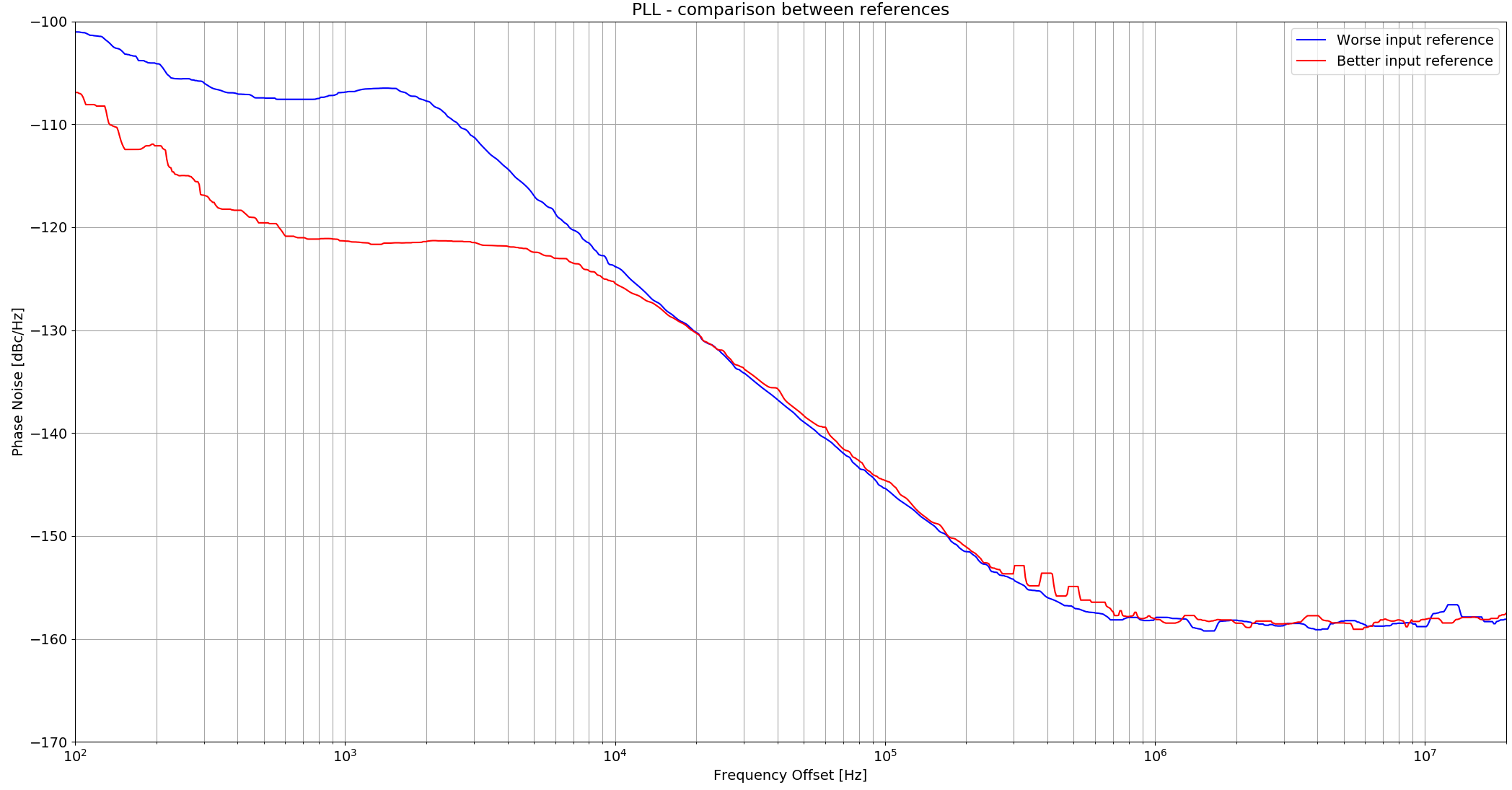

The importance of a high-quality input reference is highlighted in Fig. 6 where the phase noise of a PLL is measured comparing two references. The better reference has a 15fs jitter whereas the worse one has a 880fs jitter. It is clearly visible how the reference quality affects the PLL noise at low offset frequencies.

Figure 6: PLL phase noise comparing input references.

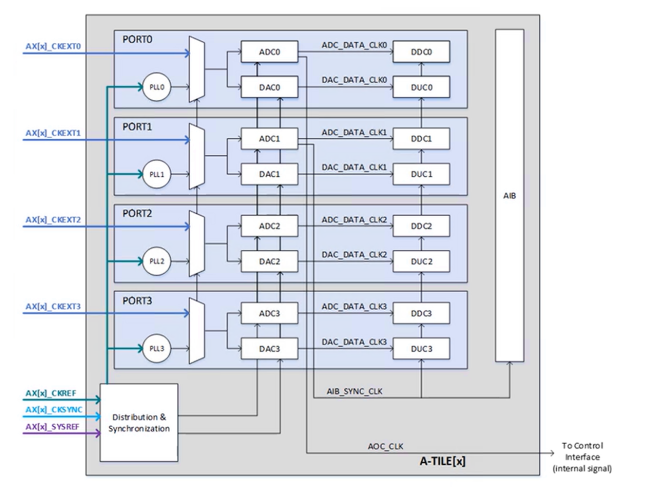

Besides its phase noise, the frequency of the reference has also a key role in shaping the overall phase noise of the PLL. In particular the following equation applies

where PNOUT is the PLL output phase noise and fOUT and fREF are the output and reference frequencies, respectively.

Therefore a higher reference frequency leads to lower output phase noise.

D. Example: Altera Stratix 10 RFSoC clocks

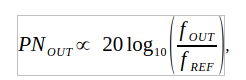

As already discussed, Direct RF FPGAs require three main clock signals to operate correctly. As an example let’s take a look at the Altera Agilex 9 RFSoC. This FPGA has a sampling frequency (Fs) between 40 and 64GSPS. The ADC and DAC sampling clock can either be generated by internal PLLs, providing a reference CLK (CKREF) or it can be directly provided, by means of CKEXT signals. CKREF can be set to either Fs/8, Fs/16 or Fs/32, therefore ranging from

1.25 GHz to 8 GHz.

If synchronization is used (see following sections), a synchronization clock (CKSYNC) and a synchronization pulse (SYSREF) also need to be provided. CKSYNC has a Fs/128 frequency, therefore ranging between 312.5MHz and 500MHz. Figure 7 shows the diagram of the clocks required by the analog part of the Altera Agilex 9 RFSoC.

Figure 7: Altera Stratix 10 RF analog clock structure.

Finally the same CKSYNC and SYSREF clocks need to be provided to the FPGA to run the RF IP logic and synchronization.

E. Effects of bad clocks to RF performance

Up to now we have assumed that high-quality clocks are required in RF systems, especially for a high-frequency direct-RF application. But what exactly are the consequences of bad clocks? The following list summarizes the main limiting factors and implications of noisy and less stable clocks:

- Reciprocal mixing happens when an unwanted RF signal, relatively close in frequency, contaminates the signal we are interested in sampling. This phenomenon occurs both in traditional heterodyne systems and in direct-RF systems, where the sampling clock acts as a local oscillator and its phase noise causes the unwanted signal to spread and contaminate the close-by target. Reciprocal mixing leads to reduced sensitivity due to the higher noise floor and reduced dynamic range as it becomes harder to handle strong and weak signals simultaneously

- Widening of transmitted signal spectrum is caused by the clock directly affecting the DAC performance in a transmitter as the clock phase noise and jitter spread the transmitted power into multiple channels. Transmission error rates are therefore increased due to spectrum widening.

- Clock jitter has a direct effect on signal to noise ratio (SNR) as shown in the following equation

where f is the input signal frequency and τ is the clock jitter. As the frequency of the input signal to be sampled increases, the jitter of the sampling clock needs to be optimized to maintain a high SNR

- Demodulation errors are enhanced by frequency drift and long-term instability of the sampling clock that cause effects such as symbol rotation and higher bit error rate (BER)

- Reduction of spurious-free dynamic range (SFDR) as clock noise causes the rise of the noise floor and the introduction of new spurs if the clock itself is affected by periodic timing modulation

- Synchronization quality is directly related to the jitter of the clock used for the synchronization. A high-jitter clock leads to a higher uncertainty in the final phase alignment of the RF channels.

F. Flexibility, consolidation and their price

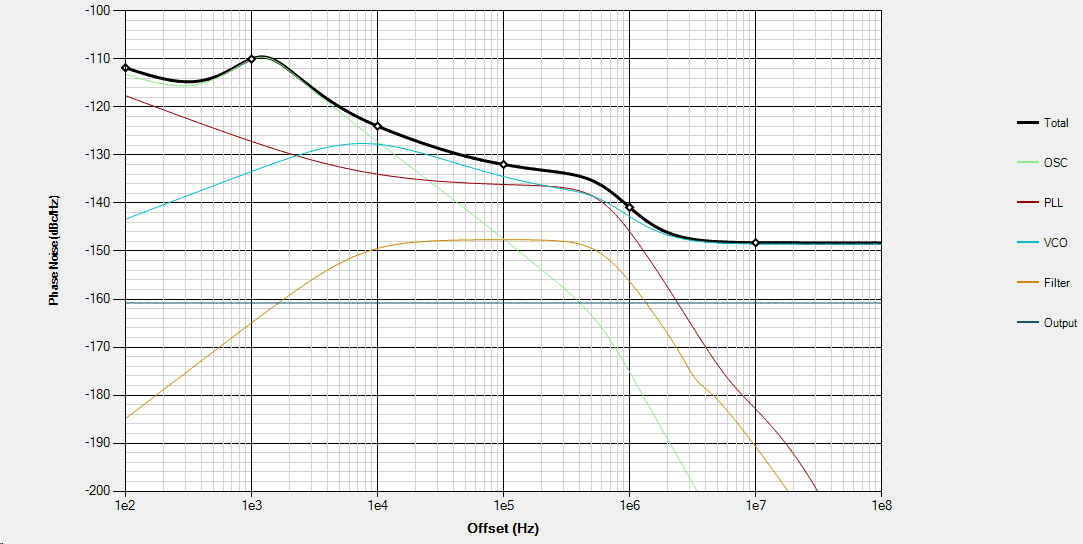

As discussed in the previous sections RF clock architectures consists of a reference and one or multiple PLLs to generate the required clock signals. Sometimes multiple PLLs are used in a chain to achieve both flexibility and high frequencies: one PLL might be used for its flexibility in generating multiple frequencies, ensuring more freedom in choosing the sampling clock frequency, and a different PLL, taking the output of the first one as input, boosts the frequency to the desired value.

The same approach can benefit the system in terms of consolidation: besides analog-related clock signals an FPGA system usually requires digital-related clocks for the digital transceivers. An intermediate PLL with multiple and flexible outputs can also be used to generate these clocks. Therefore this type of clock architecture increases the flexibility while reducing the number of parts required.

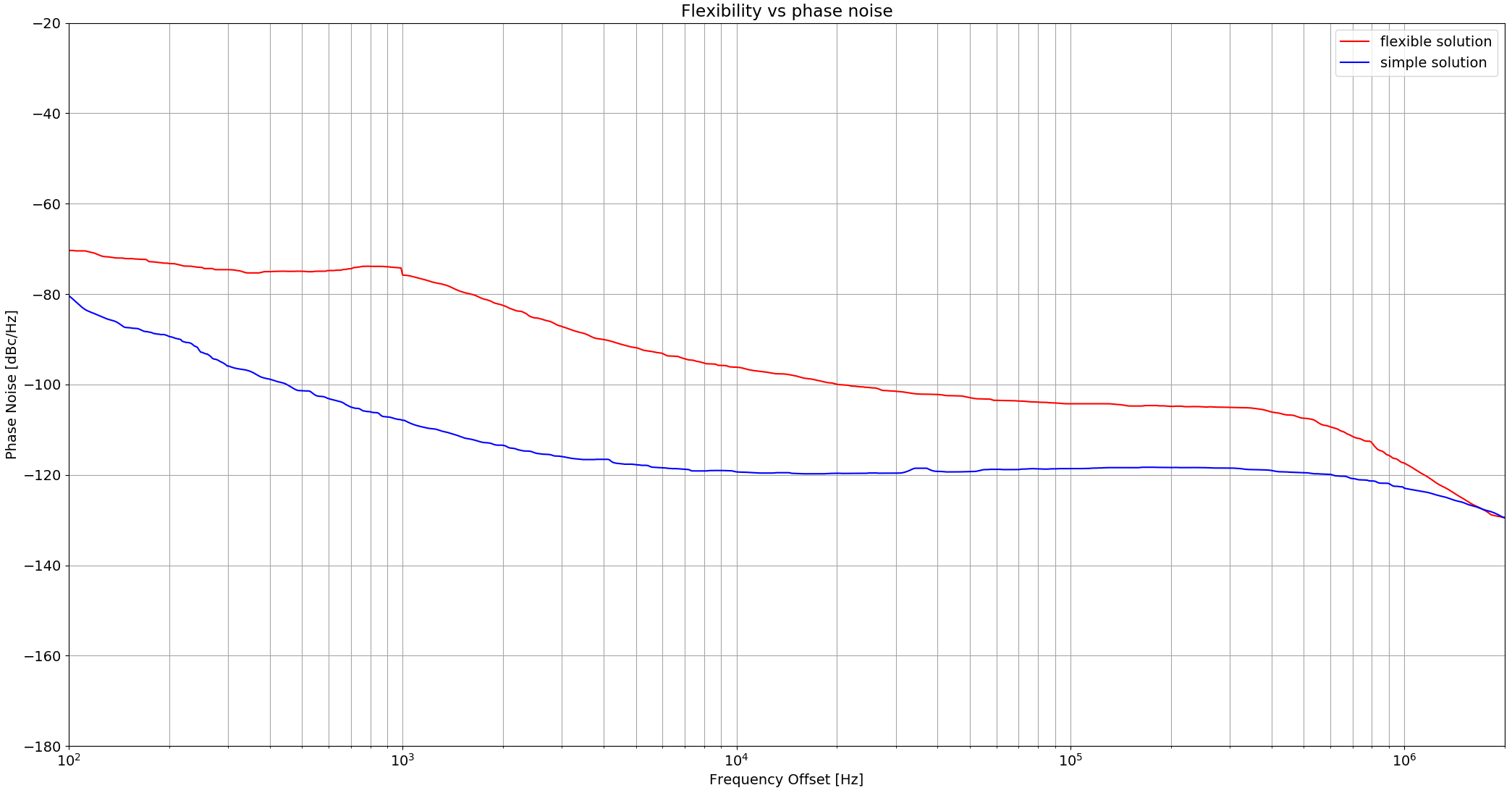

However, it is worth considering the effects of such architecture on the clock quality. Figure 8 shows the phase noise of a PLL generating a 8GHz signal, comparing two configurations: a more flexible one (red curve) where the reference output is fed into an intermediate PLL and then to the PLL under test, and a simpler one (blue curve) where the PLL is fed directly with the reference output. As can be seen, despite being more flexible and more compact, this solution shows a higher noise, leading to a x5 worse jitter with respect to the simpler configuration.

Figure 8: Phase noise of a PLL when fed directly by a clock reference (blue line) or by a different PLL (red line).

G. Synchronization: why and how

Channel synchronization is the process of time-aligning samples across multiple independent channels, both at ingress (ADC) and egress (DAC) paths. To understand why synchronization is important in RF systems let’s consider the case of a beam-forming radar system. Such systems use antenna arrays to electronically steer radar beams, achieving higher angular resolution with respect to traditional solutions, without the need of moving parts. Beam directionality is achieved by transmitting (DAC) the same signal over multiple antennas but with a different phase shift for each source. In this way signals experience constructive interference for a specific angle and destructive interference for the remaining ones, effectively creating a narrow beam. Beam forming is also adopted on the receiver side (ADC) at the digital level, where samples from the independent channels are phase shifted to achieve detection directionality in one or multiple directions. In such radar systems ensuring good synchronization is key to exploiting the full system capabilities and performance since synchronization affects, for example, the gain and directionality of the system.

When a multi-channel RF system is powered on, all ports start in an asynchronous state and will transmit or receive the same signal with different time offsets. There are two main types of time misalignment, latency and phase misalignment. Latency misalignment is due to FiFos that are responsible for clock domain crossing. Since not all channels come out of reset in the same state, there is an uncertainty in the latency. Synchronization compensates for this and ensures that all channels share the same latency. On the other hand, phase misalignment is due to internal PLLs used to generate all the required clocks and that come out of reset in a random phase relation between each other. Synchronization ensures that across all ports PLLs have a deterministic phase alignment.

To perform synchronization, two external signals are required, the synchronization clock (CKSYNC) and a pulse signal (SYSREF). CKSYNC is mainly used by the analog part to align the internal clock tree, whereas SYSREF is mainly used by the digital part to align the digital words. On the latency side, the synchronization logic computes the ingress and egress data latencies by means of DAC-to-ADC loopbacks and adds appropriate delays to each port to compensate for latency differences. On the other hand, phase alignment is achieved by providing the same CKSYNC to all channels that is then used to sample the SYSREF signal which resets the phase offsets of the internal components.

The clock architecture should also support both Multi Tile Synchronization (MTS), with different analog tiles present on the same module, and Multi Module Synchronization (MMS), with multiple modules deployed as part of the same system. MTS requires PCB length matching for RF paths and the proper CKSYNC and SYSREF signals, as discussed in our “Six Years of RFSoC Innovation” piece. MMS, on the other hand, requires more extensive planning of the clock architecture to account for system distribution and scalability. In particular, as multiple boards need to be latency and phase aligned, the same CKSYNC and SYSREF signals should be distributed to all of them taking into account all the delays in the system, from PCB traces to cable interconnects, and how to ensure a deterministic power-up sequence of the whole system.

H. Conclusions

Modern RF systems are characterized by high sampling rates, high bandwidths, low time margins and are distributed over multiple devices. All these features represent a challenge in achieving the desired precision and reliability. As we discussed in the previous sections, high-quality clock architectures are at the core of direct-RF systems and are essential to operate them at their expected capability. Therefore it is important to define the key characteristics that identify a high-quality clock and how they can be measured to build an effective clock distribution architecture, taking into account how flexibility and consolidation can affect the noise and stability performance of the system. Lastly we highlighted the key concepts of synchronization, its importance and how it is performed.

References

-

Altera Direct RF-Series FPGAs – Product Brief, Altera

-

Benefits and Challenges of Direct-RF Sampling for Avionic Platforms, Jariet Technologies

-

What is Direct RF Sampling?, EverythingRF

-

Guide to oscillator output types, ECS INC

-

Impact of Slew Rate on Noise, Texas Instruments

-

R&S FSWP Phase noise analyzer and VCO tester – product specifications, Rohde&Schwarz

-

Handbook of Frequency Stability Analysis, Riley and Howe

-

Characterization of Clocks and Oscillators, Sullivan, Allan, Howe and Walls

-

Phase-Locked Loop (PLL) Fundamentals, Analog Devices

-

RF Sampling: Clocking Is the Key Every Time, Texas Instruments

-

Impact of sampling-clock spurs on ADC performance, Texas Instruments

-

Reference Clock Considerations, Analog Devices